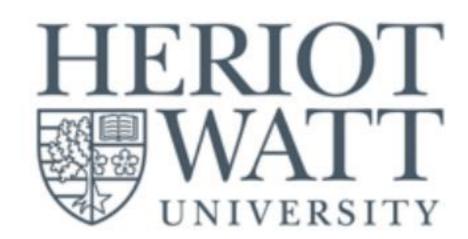

## Joint Undervolting and Overclocking Power Scaling Approximation on FPGAs

Yun Wu, João F. C. Mota, Andrew M. Wallace, Heriot-Watt University, Edinburgh, UK, {y.wu, j.mota, a.m.wallace}@hw.ac.uk

## Motivation:

- Assume we have designed an FPGA accelerator, e.g. using sensible arithmetic approximation

- Research Question: Can I reduce the supply voltage and overclock to reduce power and improve the energy efficiency?

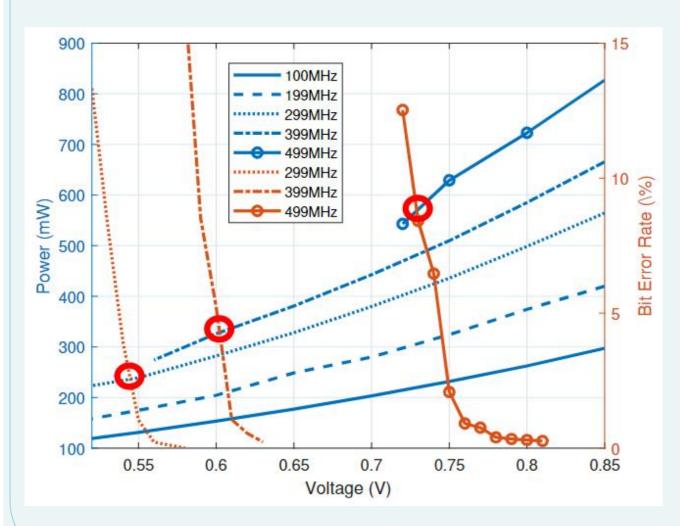

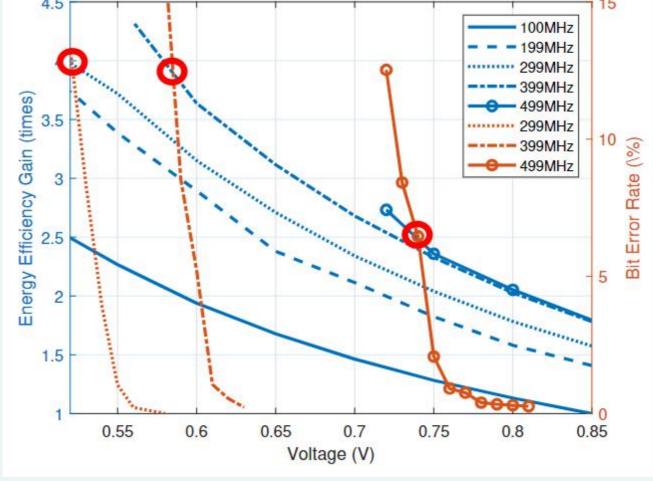

## Power & energy v.s. bit error rate against voltage & frequency

## Conclusions:

- Yes, further substantial improvements are feasible

- Up to ~60% power saving

- At least ~2.5x energy efficiency

- Bit-flipping error patterns are device and location dependent

Engineering and Physical Sciences Research Council